# **RCL Semiconductors Ltd.**

# Dual D Flip-Flops with Preset and Clear

HC74

#### **GENERAL DESCRIPTION**

HC74 is fabricated with high speed silicon gate CMOS technology. It has the high noise immunity and low power consumption of standard CMOS integrated circuits.

The HC74 devices contain two independent D-type flip-flops triggered at the positive edge of Clock (CK). A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup time requirements are transferred to the outputs on the positive-going edge of the clock (CK) pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of CK. Following the hold-time

interval, data at the D input can be changed without affecting the levels at the outputs.

The HC74 utilizes silicon gate CMOS technology to achieve operating speeds similar to the equivalent LS-TTL part. It possesses the high noise immunity and low power consumption of standard CMOS integrated circuits, along with the ability to drive 10 LS-TTL loads.

This flip-flop has independent data , preset, clear, clock inputs, Q and  $\overline{Q}$  outputs. The logic level present at the data input is transferred to the output during the positive-going transition of the clock pulse. Preset and clear are independent of the clock and accomplished by a low level at the appropriate input.

#### **FEATURES**

- Output Drive at 5V: ±4-mA

- Typical propagation delay: 15ns

- · Wide operating supply voltage range: 2-6V.

- Low input current:  $< 1 \mu A$ .

- Low quiescent supply current: 40-µA maximum.

- · Fanout of 10 LS-TTL Loads.

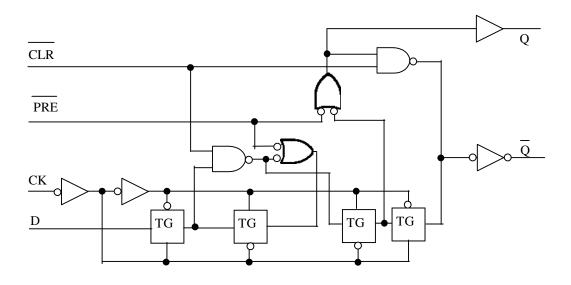

#### **LOGIC DIAGRAM**

3 Dai Fu Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. Tel: (852)-26659229 Fax: (852)-26652201

061031

### **FUNCTIONAL DESCRIPTION**

### 1. Truth Table

|     | INPUT | OUT      | PUTS |    |                           |

|-----|-------|----------|------|----|---------------------------|

| PRE | CLR   | CLK      | О    | Q  | Q                         |

| L   | Н     | Χ        | Χ    | Η  | Г                         |

| Н   | L     | Χ        | Χ    | L  | Н                         |

| L   | L     | Χ        | Χ    | Н* | Н*                        |

| Н   | Н     | <b>†</b> | Н    | Н  | L                         |

| Н   | Н     | <b>†</b> | L    | L  | Н                         |

| Н   | Н     | L        | Χ    | Q0 | $\overline{\mathbb{Q}}$ 0 |

H = High Level (steady state). L= Low Level (steady state)

X = Irrelevant (any input, including transitions)

$\uparrow$  = Transition from low to high level.

Note: Q0= the level of Q before the indicated input conditions were established.

\*: This configuration is non-stable; that is, it will not persist when preset and clear inputs return to their inactive(high) level.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                 | Value         | Unit       |

|-----------------------------------------------------------|---------------|------------|

| Supply voltage (VDD)                                      | - 0.5 ~ + 7.0 | V          |

| Input clamp current , $l_{IK}$ ( $V1 < 0$ or $V1 > VDD$ ) | ±20           | mA         |

| Output clamp current , loκ ( V0 < 0 or V0> VDD )          | ±20           | mA         |

| Continuous output current , lo (Vo = 0 to VDD )           | ±25           | mA         |

| Continuous current through VDD or VSS                     | ±50           | mA         |

| Storage temperature range , T <sub>stg</sub>              | -65 ~ +150    | $^{\circ}$ |

**Note:** 1. Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed.

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                    |                                  | Min.               | Normal | Max.               | Unit                 |

|------------------------------|----------------------------------|--------------------|--------|--------------------|----------------------|

| DC Supply Voltage (VDD)      |                                  | 2.0                | 5.0    | 6.0                | V                    |

| VIH High-level Input Voltage | VDD=2.0V<br>VDD=4.5V<br>VDD=6.0V | 1.5<br>3.15<br>4.2 |        |                    | V                    |

| VIL Low-level Input Voltage  | VDD=2.0V<br>VDD=4.5V<br>VDD=6.0V | F                  |        | 0.5<br>1.35<br>1.8 | V                    |

| V <sub>I</sub> Input Voltage | Vi Input Voltage                 |                    |        | VDD                | V                    |

| Vo Output Voltage            |                                  | 0                  |        | VDD                | V                    |

| Operating Temperature        | 74HC74                           | -40                |        | +85                | $^{\circ}\mathbb{C}$ |

| (TA)                         | 54HC74                           | -55                |        | +125               | $^{\circ}\mathbb{C}$ |

| Input Rise/Fall Times        |                                  |                    |        |                    | ns                   |

| (tr, tf)                     | VDD=2.0V                         |                    |        | 1000               |                      |

|                              | VDD=4.5V                         |                    |        | 500                |                      |

|                              | VDD=6.0V                         |                    |        | 400                |                      |

<u>Note</u>: 2. All unused inputs of the device must be held at VDD or VSS to ensure proper device operation.

## DC ELECTRICAL CHARACTERISTICS

$(T_A = 25^{\circ}C)$

| Parameter       | Symbol   | Unit | Тур.      | Guaranteed<br>Limit | VDD    | Test (                    | Condition                           |

|-----------------|----------|------|-----------|---------------------|--------|---------------------------|-------------------------------------|

| Minimum High    | Voh      | V    | VDD-0.002 | VDD-0.1             | 2V     | I <sub>OH</sub> = -20 µ A | $V_I = V_{IH} \text{ or } V_{IL}$   |

| Level Output    |          |      | VDD-0.001 | VDD-0.1             | 4.5~6V |                           |                                     |

| Voltage         |          |      | 4.3       | 3.98                | 4.5V   | Iон = -4 mA               |                                     |

|                 |          |      |           | 3.7                 |        | (54HC)                    |                                     |

|                 |          |      |           | 3.84                |        | (74HC)                    |                                     |

|                 |          |      | 5.8       | 5.48                | 6V     | $I_{OH} = -5.2 mA$        |                                     |

|                 |          |      |           | 5.2                 |        | (54HC)                    |                                     |

|                 |          |      |           | 5.34                |        | (74HC)                    |                                     |

| Maximum Low     | $V_{OL}$ | V    | 0.002     | 0.1                 | 2V     | $I_{OL} = 20 \mu A$       | $V_{I} = V_{IH} \text{ or } V_{IL}$ |

| Level Output    | ;        |      | 0.001     | 0.1                 | 4.5~6V |                           |                                     |

| Voltage         |          |      | 0.17      | 0.26                | 4.5V   | $I_{OL} = 4 \text{ mA}$   |                                     |

|                 |          |      |           | 0.4                 |        | (54HC)                    |                                     |

|                 |          |      |           | 0.33                |        | (74HC)                    |                                     |

|                 |          |      | 0.15      | 0.26                | 6V     | $I_{OL} = 5.2 \text{ mA}$ |                                     |

|                 |          |      |           | 0.4                 |        | (54HC)                    |                                     |

|                 |          |      |           | 0.33                |        | (74HC)                    |                                     |

| Maximum Input   | $I_{I}$  | nA   | ±0.1      | ±100                | 6V     |                           | $V_I = VDD \text{ or } 0$           |

| Current         |          |      |           | ±1000               |        | (54/74HC)                 |                                     |

| Maximum         | Icc      | μА   | -         | 2                   | 6V     | $V_I = VDD \text{ or } 0$ | $I_0 = 0$                           |

| Supply Current  |          |      |           | 40                  | (54HC) |                           |                                     |

|                 |          |      |           | 20                  | (74HC) |                           |                                     |

|                 | Ci       | pF   | 3         | 10                  | 2V~6V  |                           |                                     |

| Power           | Cpd      | pF   | 35        |                     |        | No load                   |                                     |

| Dissipation     |          |      |           |                     |        |                           |                                     |

| capacitance per |          |      |           |                     |        |                           |                                     |

| FLIP-FLOP       |          |      |           |                     |        |                           |                                     |

# AC ELECTRICAL CHARACTERISTICS(timing requirements)

(CL=50pF,  $T_A = 25^{\circ}C$ )

| F                         | Parameter           | Symbol | Unit | Guaranteed<br>Limit | 54HC | 74HC | VDD  |

|---------------------------|---------------------|--------|------|---------------------|------|------|------|

| Clock frequency           |                     | fclock | MHz  | 6                   | 4.2  | 5    | 2V   |

|                           |                     |        |      | 31                  | 21   | 25   | 4.5V |

|                           |                     |        |      | 36                  | 25   | 29   | 6V   |

| Pulse duration            |                     | tw     | ns   | 100                 | 150  | 125  | 2V   |

|                           | PRE or CLR low      |        |      | 20                  | 30   | 25   | 4.5V |

|                           |                     |        |      | 17                  | 25   | 21   | 6V   |

|                           | CK high or low      |        |      | 80                  | 120  | 100  | 2V   |

|                           |                     |        |      | 16                  | 24   | 20   | 4.5V |

|                           |                     |        |      | 14                  | 20   | 17   | 6V   |

| Setup time                | Data                | tsu    | ns   | 100                 | 150  | 125  | 2V   |

| before CK 1               |                     |        |      | 20                  | 30   | 25   | 4.5V |

|                           |                     |        |      | 17                  | 25   | 21   | 6V   |

|                           |                     |        |      | 25                  | 40   | 30   | 2V   |

|                           | PRE or CLR inactive |        |      | 5                   | 8    | 6    | 4.5V |

|                           |                     |        |      | 4                   | 7    | 5    | 6V   |

| Hold time, data after CK↑ |                     | th     | ns   | 0                   | 0    | 0    | 2~6V |

## **AC ELECTRICAL CHARACTERISTICS**

| Parameter | Symbol     | Typ. | Unit |       | 54HC | 74HC | VDD  |            |        |

|-----------|------------|------|------|-------|------|------|------|------------|--------|

|           |            |      |      | Limit |      |      |      | From       | То     |

| Maximum   | fmax       | 10   | MHz  | 6     | 4.2  | 5    | 2V   |            |        |

| Clock     |            | 50   |      | 31    | 21   | 25   | 4.5V |            |        |

| Frequency |            | 60   |      | 36    | 25   | 29   | 6V   |            |        |

|           | tpd        | 70   | ns   | 230   | 345  | 290  | 2V   |            | _      |

|           |            | 20   |      | 46    | 69   | 58   | 4.5V | PRE or CLR | Q or Q |

|           |            | 15   |      | 39    | 59   | 49   | 6V   |            |        |

|           |            | 70   |      | 175   | 250  | 220  | 2V   |            |        |

|           |            | 20   |      | 35    | 50   | 44   | 4.5V | CK         | Q or Q |

|           |            | 15   |      | 30    | 42   | 37   | 6V   |            |        |

| transmit  | <b>t</b> t | 28   | ns   | 75    | 110  | 95   | 2V   |            | _      |

| time      |            | 8    |      | 15    | 22   | 19   | 4.5V |            | Q or Q |

|           |            | 6    |      | 13    | 19   | 16   | 6V   |            |        |

<u>Note</u>: 3.  $C_{PD}$  determines the no load dynamic power consumption,  $P_D = C_{PD} \ VDD^2 f + Icc \ VDD$ , and the no load dynamic current consumption,  $I_S = C_{PD} \ VDD^f + Icc$ .

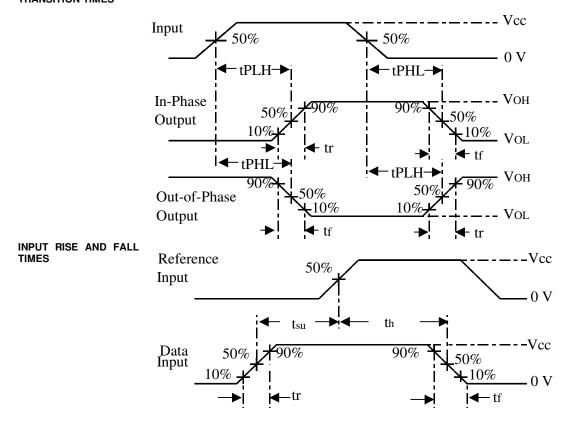

## AC SWITCHING WAVEFORM AND AC TEST CIRCUIT

VOLTAGE WAVEFORMS PROPAGATION DELAY AND OUTPUT TRANSITION TIMES

Notes:

- a. CL includes probe and test-fixture capacitance.

- b. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR≤1MHz, Zo=50 Ω, tr=tf=6ns.

- c. The outputs are measured one at a time with one input transition per measurement. tplh and tphl are the same as tpd.

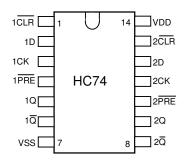

### **PIN DESCRIPTION**

| PIN NO.    | SYMBOL                              | DESCRIPTION           |

|------------|-------------------------------------|-----------------------|

| 2, 12      | 1D, 2 <u>D</u>                      | Data Inputs           |

| 5, 6, 8, 9 | 1Q, 1Q, 2Q, 2Q                      | Outputs               |

| 7          | VSS                                 | Ground (0V)           |

| 3, 11      | 1CK, 2CK                            | Clock input           |

| 1, 13      | 1 <del>CLR</del> , 2 <del>CLR</del> | Clear                 |

| 4, 10      | 1PRE, 2PRE                          | PRESET                |

| 14         | VDD                                 | Positive power supply |

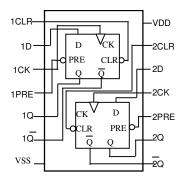

Pin Configuration

Logic Symbol

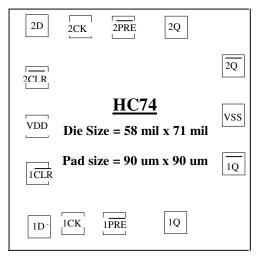

### PAD DIAGRAM

### The Coordinate of Each Pad

| 1D (-425.5, 450.3)   | 2Q(106.5, 355.9)     |

|----------------------|----------------------|

| 1CK (-284.1, -445.9) | 2PRE(-142.9, 355.9)  |

| 1PRE (-142.9,-445.9) | 2CK (-284.1, 355.9)  |

| 1Q (106.9, -445.9)   | 2D(-425.5, 360.3)    |

| 1Q (351.4, -298.4)   | 2CLR(-425.7,114.3)   |

| VSS (351.4,- 45.0)   | VDD(-423.5, -46.1)   |

| 2Q (351.4, 208.4)    | 1CLR(-425.5, -204.3) |

|                      |                      |

**Note:** Substrate should be connected to VDD or left it open.